Vergleich zwischen SOI und Silizium-Wafern: Was ist das Beste für Ihr Halbleiterprojekt?

1 Einleitung

SOI ist ein Halbleitermaterial mit einer geschichteten Siliziumschicht-Isolierschicht-Siliziumsubstrat-Struktur. Im Vergleich zu Siliziumwafern, die üblicherweise in Halbleiterbauelementen verwendet werden, gibt es erhebliche Unterschiede zwischen den beiden in Bezug auf die Materialstruktur, die Leistungsmerkmale, die Anwendungsbereiche usw.

Die SOI-Struktur verbessert die Leistung und Zuverlässigkeit des Bauelements durch die Schichtstruktur Siliziumschicht-Isolierschicht-Siliziumsubstrat, aber die Herstellungskosten sind höher. Die herkömmlichen Siliziumwafer hingegen haben niedrigere Herstellungskosten und eignen sich für eine breite Palette von integrierten Schaltungen.

![]()

2 Was ist SOI?

SOI steht für Silicon-On-Insulator. Bei SOI wird die Oberfläche eines Siliziumchips mit einem isolierenden Material (in der Regel Siliziumdioxid) bedeckt, auf das dann eine Siliziumschicht aufgewachsen wird. Auf diese Weise entsteht eine Schichtstruktur aus Siliziumschicht, Isolierschicht und Siliziumsubstrat.

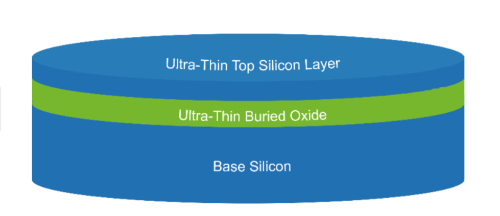

2.1 Der Aufbau von SOI

Die Struktur eines SOI (Silicon-On-Insulator) besteht aus den folgenden Hauptbestandteilen:

- Si-Schicht: Auf der SOI-Struktur befindet sich eine Schicht aus Siliziumkristallen (Si), die in der Regel die gewünschten elektronischen Eigenschaften und Bauelementeigenschaften aufweisen. Diese Schicht kann mit Standard-Silizium-Wafer-Wachstumstechniken hergestellt werden.

- Isolierende Schicht: Unter der Si-Schicht befindet sich ein isolierendes Material, in der Regel Siliziumdioxid (SiO2). Der Zweck der Isolierschicht besteht darin, die darüber liegende Siliziumschicht vom darunter liegenden Siliziumsubstrat zu isolieren und so das Übersprechen zwischen den Transistoren zu verringern.

- Silizium-Substrat: Das Siliziumsubstrat bildet die Unterseite der SOI-Struktur und ist in der Regel das wichtigste Trägersubstrat für den Wafer. Das Siliziumsubstrat besteht in der Regel aus kristallinem Silizium, das der SOI-Struktur mechanischen Halt und Stabilität verleiht.

2.2 Die Klassifizierung von SOI

Es gibt mehrere verschiedene Varianten der SOI-Technologie. SOI lassen sich je nach ihrer Struktur und ihrem Zweck nach verschiedenen Kriterien einteilen.

2.2.1 Klassifizierung nach Art der Struktur

Gemeinsame SOI (c-SOI): Common SOI ist eine der gebräuchlichsten SOI-Strukturen, die auch als Full SOI bezeichnet wird. Sie nutzt die übliche SOI-Fertigungsmethode, bei der eine isolierende Schicht (in der Regel Siliziumdioxid) auf die Oberfläche eines Siliziumwafers aufgebracht wird, auf der dann eine Siliziumschicht wächst. Bei einer gewöhnlichen SOI ist die Dicke der Siliziumschicht in der Regel vergleichbar mit der Dicke der Isolierschicht, so dass eine Struktur aus Siliziumschicht, Isolierschicht und Siliziumsubstrat entsteht.

Partielles SOI (p-SOI): Partielles SOI unterscheidet sich von regulärem SOI dadurch, dass die Dicke der Siliziumschicht dünner ist, nur ein Bruchteil der Dicke der Isolierschicht. Bei einem partiellen SOI ist die Dicke der Siliziumschicht in der Regel geringer als die Dicke der Isolierschicht, wodurch die partielle SOI-Struktur eine dünnere Siliziumschicht aufweist.

Umgekehrte SOI (r-SOI): Reverse SOI ist eine spezielle SOI-Struktur, die sich von der normalen SOI und der partiellen SOI unterscheidet. Bei Reverse SOI wird die Siliziumschicht vom Substrat entfernt und wieder mit der Isolierschicht verbunden. Bei dieser Struktur befindet sich der Transistor oberhalb der Isolierschicht und das Siliziumsubstrat unterhalb der Isolierschicht, wodurch sich die Topologie der herkömmlichen SOI-Struktur ändert.

Diese verschiedenen SOI-Varianten bieten unterschiedliche Vorteile und Einsatzmöglichkeiten für bestimmte Anwendungen. Gewöhnliche SOI werden üblicherweise in Hochleistungs- und Niedrigstromanwendungen eingesetzt, während partielle SOI besser für bestimmte Hochfrequenzbauelemente geeignet sind und invertierte SOI zusätzliche Vorteile für bestimmte Anwendungen bieten, z. B. für Hochgeschwindigkeitsbauelemente mit geringem Verlust.

2.2.2 Klassifizierung nach Kristall-Substrat-Typ

Silizium-auf-Isolator (SIMOX-SOI): SIMOX (Separation by IMplantation of OXygen) ist eine gängige Methode der SOI-Herstellung, auch bekannt als Silicon-on-Insulator. Bei der SIMOX-SOI-Herstellung werden Sauerstoffionen in den Wafer injiziert und anschließend wärmebehandelt, damit die Sauerstoffionen eine isolierende Schicht aus Siliziumoxid im Wafer bilden, was zur Bildung der SOI-Struktur führt.

Ultradünnes SOI (UTSOI): Ultra-Thin SOI ist eine spezielle Art von SOI-Struktur, die sich durch eine sehr dünne Siliziumschicht auszeichnet, die in der Regel zwischen einigen Nanometern und einigen zehn Nanometern liegt. Bei der Herstellung von UTSOI werden in der Regel spezielle Wachstums- oder Ablösetechniken angewandt, um eine sehr dünne Siliziumschicht auf einem Siliziumsubstrat zu bilden und die SOI-Struktur zu realisieren.

Epitaktische SOI (Epi-SOI): Epi-SOI ist eine Methode zur Herstellung von SOI-Strukturen durch Aufwachsen einer epitaktischen Siliziumschicht auf einem Siliziumsubstrat. Bei Epi-SOI wird die epitaktische Siliziumschicht auf einem Siliziumsubstrat aufgewachsen und hat in der Regel dieselbe Kristallstruktur wie das Substrat, jedoch mit einer isolierenden Schicht zwischen der Siliziumschicht und dem Substrat.

SIMOX-SOI wird üblicherweise bei der Herstellung von integrierten Schaltkreisen verwendet, UTSOI wird üblicherweise für Anwendungen mit hoher Leistung und geringem Stromverbrauch, z. B. in der Mobilkommunikation und bei HF-Geräten, eingesetzt, während Epi-SOI eine bessere Kristallqualität und strukturelle Kontrolle für spezielle Anforderungen bei der Herstellung von Geräten bietet.

2.2.3 Klassifizierung nach der Dicke der Siliziumschicht

Dünnschicht-SOI : Bei Dünnschicht-SOI liegt die Dicke der Siliziumschicht in der Regel zwischen einigen zehn und einigen hundert Nanometern. Diese Art von SOI-Struktur wird häufig für die Herstellung von ultradünnen Bauelementen verwendet, z. B. für elektronische Bauelemente mit geringem Stromverbrauch, optoelektronische Bauelemente usw. Dünnschicht-SOI werden in der Regel mit einer Reihe von Präzisionsbearbeitungsschritten hergestellt, darunter Techniken wie chemisch-mechanisches Polieren (CMP), Wasserstoffioneninjektion und Strippen.

Dickschicht-SOI: Bei Dickschicht-SOI beträgt die Dicke der Siliziumschicht in der Regel mehrere hundert Nanometer oder mehr. Diese Art von SOI-Struktur wird in der Regel für die Herstellung herkömmlicher integrierter Schaltungen wie Mikroprozessoren, Speicher usw. verwendet. Dickschicht-SOIs werden in der Regel mit verschiedenen Techniken wie SIMOX, Unibond und Smart Cut hergestellt. Diese Techniken ermöglichen die Herstellung von Siliziumschichten mit großen Dicken, um den Anforderungen der herkömmlichen Herstellung integrierter Schaltkreise gerecht zu werden.

2.2.4 Klassifizierung nach der Ladungskontrollmethode für Transistoren

Vollständig verarmtes SOI (FD-SOI): Bei FD-SOI befindet sich die gesamte Siliziumschicht in einem verarmten Zustand, was bedeutet, dass die Ladung des Transistors vollständig durch das darüber liegende Gate gesteuert wird und nicht durch das untere Substrat beeinflusst wird. Durch die genaue Steuerung der Dicke der Siliziumschicht und der Eigenschaften der Isolierschicht ist es möglich, eine gesamte Siliziumschicht in einem verarmten Zustand zu erreichen. Diese Struktur bietet eine bessere Ladungskontrolle und einen geringeren Leckstrom. Vollständig verarmtes SOI wird häufig als Halbleitertechnologie der nächsten Generation mit höherer Leistung und geringerem Stromverbrauch angesehen und findet daher immer mehr Beachtung bei der Entwicklung und Herstellung von Chips.

Teilweise verarmtes SOI (pFD-SOI): Bei teilweise verarmtem SOI befindet sich ein Teil der Siliziumschicht in einem verarmten Zustand, während ein anderer Teil in einem nicht verarmten Zustand bleibt. Mit einem geeigneten Design und Prozess ist es in der Regel möglich, nur einen Teil der Siliziumschicht (in der Regel den oberen Teil) in einem verarmten Zustand zu halten. Teilweise verarmtes SOI kann in Hochleistungsanwendungen mit geringem Stromverbrauch eingesetzt werden, z. B. in der Mobilkommunikation, in Hochfrequenzgeräten und in anderen Bereichen. Es bietet Möglichkeiten für eine bessere Ladungssteuerung und Leistungsoptimierung.

Die nachstehende Tabelle zeigt die verschiedenen SOI-Strukturen, ihre charakteristischen Merkmale und ihre typischen Anwendungen und gibt einen umfassenden Überblick über die Unterschiede zwischen den einzelnen SOI-Typen.

Stanford Advanced Materials (SAM) und andere zuverlässige Lieferanten bieten SOI-Wafer in verschiedenen Größen und Typen an. Diese Auswahl ist auf Ihre genauen Spezifikationen zugeschnitten.

Tabelle 1 Vergleich der verschiedenen Arten von SOI-Wafern

|

Klassifizierung |

Typ |

Kurzbeschreibung und Anwendungen |

|

Art der Struktur |

c-SOI |

Dicke der Siliziumschicht ähnlich der Isolierschicht. Wird in Hochleistungsanwendungen mit geringem Stromverbrauch verwendet. |

|

p-SOI |

Dünnere Siliziumschicht im Vergleich zur Isolierschicht. Geeignet für die Herstellung spezieller RF-Bauteile. |

|

|

r-SOI |

Siliziumschicht, die über der Isolierschicht angebracht ist, wodurch die Struktur invertiert wird. Für Hochgeschwindigkeitsbauelemente mit geringen Verlusten. |

|

|

Kristall-Substrat-Typ |

SIMOX-SOI |

Sauerstoffionen bilden eine isolierende Schicht aus Siliziumoxid. Üblich in der IC-Fertigung. |

|

UTSOI |

Ultradünne Siliziumschicht für Hochleistungsanwendungen mit geringem Stromverbrauch wie Mobil- und RF-Geräte. |

|

|

Epi-SOI |

Auf einem Siliziumsubstrat gewachsene Epitaxieschicht für Geräte, die eine bessere Kristallqualität benötigen. |

|

|

Dicke der Siliziumschicht |

Dünnschicht-SOI |

Zehn bis Hunderte von Nanometern dicke Siliziumschicht. Für elektronische und optoelektronische Geräte mit geringem Stromverbrauch. |

|

Dickschicht-SOI |

Mehrere hundert Nanometer dicke Siliziumschicht. Wird in herkömmlichen IC-Bauteilen wie Mikroprozessoren verwendet. |

|

|

Ladungssteuerungsverfahren für Transistoren |

FD-SOI |

Die gesamte Siliziumschicht wird für eine vollständige Ladungssteuerung verarmt. Zielt auf hochleistungsfähige, stromsparende Technologien der nächsten Generation ab. |

|

pFD-SOI |

Teilweise Verarmung der Siliziumschicht. Angewandt in Hochleistungsanwendungen mit geringem Stromverbrauch (z. B. Mobilfunk, RF). |

3 SOI versus Silizium-Wafer, was ist besser?

Die Silicon-on-Insulator (SOI)-Technologie und die traditionellen Siliziumwafer haben die Landschaft der Halbleiterherstellung lange Zeit entscheidend geprägt, wobei beide unterschiedliche strukturelle Eigenschaften und Leistungsmerkmale aufweisen. Da die Nachfrage nach effizienteren, schnelleren und kleineren elektronischen Geräten steigt, ist es wichtig, die Unterschiede zwischen diesen beiden grundlegenden Materialien zu verstehen. Dieser Vergleich soll die strukturellen Nuancen und Leistungsergebnisse von SOI- und Silizium-Wafern aufzeigen.

3.1 Wie sich SOI- und Silizium-Wafer in ihrer Struktur unterscheiden

Silizium-Wafer: Ein herkömmlicher Siliziumwafer besteht aus einem einzigen Siliziumkristall und einer monokristallinen Siliziumstruktur. Bei einem herkömmlichen Siliziumwafer besteht die Oberfläche des Wafers in der Regel aus einem einzigen Siliziumkristall ohne zusätzliche Isolierschicht. Siliziumwafer haben eine einfache Struktur und sind das gängigste Substrat für Halbleiterbauelemente.

SOI: Bei der SOI-Struktur ist die Oberfläche des Siliziumwafers mit einer Schicht aus isolierendem Material (meist Siliziumdioxid) bedeckt. Diese Isolierschicht wird in der Regel verwendet, um die Siliziumschicht vom Siliziumsubstrat zu isolieren und so das Übersprechen zwischen den Bauelementen zu verringern und die Leistung und Zuverlässigkeit der Bauelemente zu verbessern. Auf der Isolierschicht wird eine weitere Siliziumschicht aufgewachsen, um eine Schichtstruktur aus Siliziumschicht - Isolierschicht - Siliziumsubstrat zu bilden. Die Siliziumschicht ist die aktive Schicht des Transistors und weist in der Regel die gewünschten elektronischen Eigenschaften und die Leistung des Bauelements auf. Die Dicke der Isolierschicht kann je nach den Anforderungen der Anwendung angepasst werden, um die Eigenschaften und die Leistung des Bauelements zu steuern.

SOIs haben im Vergleich zu herkömmlichen Siliziumwafern eine zusätzliche Isolierschicht. Das Vorhandensein dieser Isolierschicht verbessert die Leistung und Zuverlässigkeit der Bauelemente, erhöht aber auch die Komplexität und die Kosten der Herstellung.

3.2 Leistungsunterschiede zwischen SOI- und Silizium-Wafern

- Unterdrückung von Nebensprechen: Jeder Transistor in der SOI-Struktur ist durch eine Isolierschicht isoliert, wodurch das Übersprechen zwischen den Bauteilen erheblich reduziert wird. Durch das Vorhandensein der Isolierschicht wird die elektromagnetische Kopplung zwischen den Transistoren verringert, was die Leistung und Zuverlässigkeit des Bauelements verbessert. Übersprechen ist in der Regel ein ernsthaftes Problem bei integrierten Schaltungen mit hoher Dichte, und die Verwendung von SOIs reduziert die Auswirkungen des Übersprechens auf die Leistung der Bauelemente wirksam.

- Vorteile bei Geschwindigkeit und Stromverbrauch: SOI-Bauelemente haben in der Regel eine höhere Geschwindigkeit und eine geringere Leistungseffizienz. Aufgrund des geringeren Widerstands gegen Ladungsbewegungen in der SOI-Struktur können sich die Elektronen in der Siliziumschicht schneller bewegen, was zu höheren Schaltgeschwindigkeiten und geringerem Stromverbrauch führt. Dies verschafft SOI einen klaren Vorteil bei Anwendungen mit hoher Leistung und geringem Stromverbrauch, z. B. in der mobilen Kommunikation und bei Hochleistungsrechnern.

- Verbesserte Strahlungsbeständigkeit: Die SOI-Struktur verbessert die Strahlungsresistenz des Bauelements, wodurch es sich besser für Anwendungen in Umgebungen mit hoher Strahlung eignet. Durch das Vorhandensein einer Isolierschicht sind SOI-Bauteile weniger strahlungsempfindlich und haben daher ein breites Anwendungsspektrum in der Raumfahrt, in Kernkraftwerken und anderen elektronischen Geräten in strahlungsintensiven Umgebungen. Die verbesserte Strahlungsbeständigkeit ist für einige spezielle Anwendungen wie Raumfahrt und Kernenergie von entscheidender Bedeutung.

3.3 Wie SOI und Siliziumwafer verwendet werden

--SOI-Anwendungsbereiche

Leistungsstarke Anwendungen: SOI wird häufig in Anwendungen eingesetzt, die eine hohe Leistung erfordern, z. B. in Hochgeschwindigkeits-Computerchips und Grafikprozessoren. Seine niedrige Ladungsbewegungsimpedanz und seine Eigenschaften zur Unterdrückung von Übersprechen machen es ideal für die Realisierung hoher Leistungen.

Anwendungen mit niedrigem Stromverbrauch: Da SOI-Bauteile einen geringeren Stromverbrauch und höhere Schaltgeschwindigkeiten aufweisen, haben sie ein breites Anwendungsspektrum in Bereichen wie mobilen Geräten und drahtlosen Sensornetzwerken, die einen geringen Stromverbrauch erfordern. Zum Beispiel werden Chips in Geräten wie Smartphones und Tablet-PCs häufig mit SOI-Technologie ausgestattet.

Hochfrequenz (RF)-Anwendungen: Die hohe Geschwindigkeit und die geringen Verluste von SOI sind ein großer Vorteil bei Hochfrequenzanwendungen (RF). SOI-Bauelemente können beispielsweise zur Herstellung von leistungsstarken RF-Frontend-Modulen, Antennenschaltern, Leistungsverstärkern und mehr verwendet werden.

Anwendungen in Umgebungen mit hoher Strahlung: Die SOI-Struktur verbessert die Strahlungsbeständigkeit des Bauelements, was es für Anwendungen im Weltraum, in Kernkraftwerken und anderen strahlungsintensiven Umgebungen wichtig macht. Zum Beispiel verwenden Weltraumsonden, Satellitenkommunikationssysteme und andere Geräte, die in einer Umgebung mit hoher Strahlung arbeiten müssen, häufig die SOI-Technologie.

-Traditionelle Siliziumwafer-Anwendungen

Herkömmliche Siliziumwafer werden in großem Umfang für die Herstellung verschiedener integrierter Schaltungen verwendet, darunter Mikroprozessoren, Speicher, Sensoren usw. Siliziumwafer sind die Grundlage für die Herstellung integrierter Schaltungen (ICs). Verschiedene Arten von ICs, darunter Mikroprozessoren, Speicher, analoge Schaltungen, digitale Schaltungen usw., werden durch Aufschichten verschiedener Materialien und Schaltungen auf Siliziumwafern hergestellt. Fast alle elektronischen Geräte verwenden Chips, die auf herkömmlichen Siliziumscheiben hergestellt werden, z. B. Personalcomputer, Haushaltsgeräte und elektronische Systeme für Kraftfahrzeuge. Es kann auch zur Herstellung einer Vielzahl von elektronischen Geräten verwendet werden, die in der Industrie, in Solarzellen und in biomedizinischen Geräten zum Einsatz kommen. Aufgrund der ausgezeichneten Halbleitereigenschaften sowie der ausgereiften Produktionsprozesse und der stabilen Qualitätskontrolle werden Siliziumwafer in der Produktion und in der Forschung weit verbreitet, und auch die technologische Schwelle ist im Vergleich zu SOI niedriger.

3.4 Wie SOI und Siliziumwafer hergestellt werden

--SOI-Kristallherstellungsmethoden

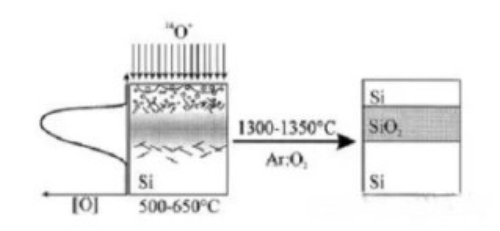

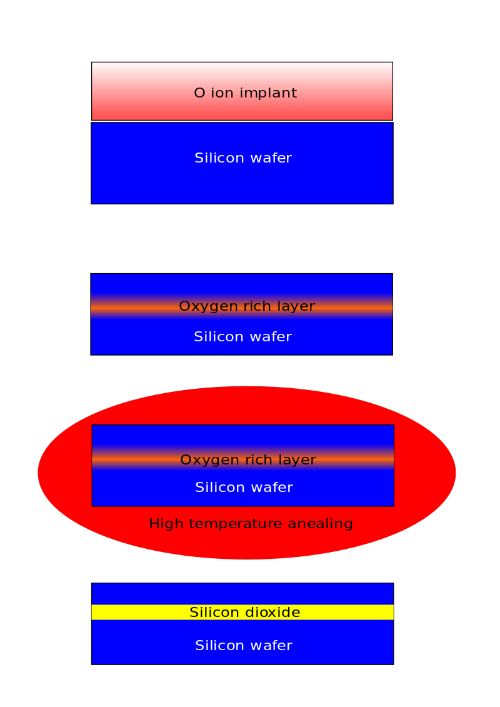

3.4.1 SIMOX-Verfahren

DieSIMOX-Technologie, kurz für Separation by IMplantation of OXygen, gilt als eine der bahnbrechenden Methoden zur Herstellung von SOI-Wafern (Silicon-On-Insulator). Diese Technik nutzt die Ionenimplantation, um Sauerstoffionen in das Silizium einzubringen und eine vergrabene Oxid-Isolationsschicht zu bilden. Diese vergrabene Oxidschicht isoliert das Substrat effektiv von der oberen Silizium-Dünnschicht. Bei dem Verfahren werden Sauerstoffionen mit einer Energie von 200 keV und einer Dosis von 1,8 × 10^18 cm^-2 in den Siliziumwafer unterhalb der Oberfläche injiziert. Anschließend werden in einem 3 bis 6 Stunden dauernden Hochtemperatur-Glühprozess bei 1350 °C chemische Reaktionen zwischen den Sauerstoffionen und den Siliziumatomen innerhalb des Wafers ermöglicht, die zur Bildung einer isolierenden Siliziumdioxidschicht mit einer Dicke von weniger als 240 nm unter der Oberfläche führen. Über dieser Isolierschicht bildet sich eine kristalline Siliziumschicht, so dass die SOI-Struktur aus Silizium-Dünnschicht - Siliziumdioxid-Isolierschicht - Siliziumsubstrat entsteht.

Zu den Vorteilen der SIMOX-Technologie gehört die Bildung einer relativ gleichmäßigen Buried Oxide (BOX)-Schicht. Die Dicke der Siliziumschicht auf der BOX kann durch Steuerung der Injektionsenergie genau kontrolliert werden. Außerdem bleibt die Schnittstelle zwischen der BOX und der oberen Siliziumschicht bemerkenswert flach.

Allerdings hat die SIMOX-Technologie auch ihre Grenzen. Der Bereich für die Einstellung der Dicke der BOX und der oberen Siliziumschicht ist relativ begrenzt. In der Regel beträgt die Dicke der BOX nicht mehr als 240 nm, da zu dünne Schichten zu einem Durchbruch zwischen der oberen Schicht und dem Substrat führen können, was mit einer erhöhten parasitären Kapazität einhergeht. Auch die Dicke der obersten Siliziumschicht ist in der Regel auf 300 nm begrenzt, was ein kostspieliges epitaktisches Siliziumwachstum und eine anschließende chemisch-mechanische Polierbehandlung (CMP) zur Glättung erforderlich macht. Außerdem kann SIMOX die Oberflächenschicht beschädigen, und die Kristallqualität der oberen Siliziumschicht entspricht möglicherweise nicht der von einkristallinem Silizium. Außerdem ist die Kristallqualität des vergrabenen SiO2 schlechter als die durch thermische Oxidation erreichte. Die Anwendung von SIMOX erfordert spezielle Ionenimplantationsanlagen, wie z. B. teure Großstrahl-Sauerstoffinjektionsmaschinen, sowie langwierige Hochtemperatur-Glühprozesse, was zu höheren Produktionskosten führt.

3.4.2 BESOI-Technologie

Bei derBESOI-Technologie (Bond and Etch Back Silicon-On-Insulator) werden zwei Wafer eng aneinander geklebt, wobei eine Siliziumdioxidschicht als vergrabene Oxidschicht zwischen ihnen entsteht. Anschließend wird mit Hilfe der Back-Engraving-Technologie die Dicke eines Wafers genau angepasst, um die gewünschte Dicke für die SOI-Wafer zu erhalten.

Das BESOI-Verfahren beginnt mit der Behandlung eines Wafers (Wafer A) durch thermische Oxidation, wodurch eine Oxidschicht entsteht, während der andere Wafer (Wafer B) bei niedriger Temperatur mit der oxidierten Oberfläche von Wafer A verbunden wird. Dieser als Silicon Fusion Bonding (SFB) bezeichnete Verbindungsprozess umfasst mehrere Schritte:

Hydrophile Behandlung: Beide Wafer werden einer hydrophilen Behandlung bei niedriger Temperatur (400°C) unterzogen, um die Bildung von Hydroxylbindungen (OH) auf ihren Oberflächen zu induzieren.

Bindung durch Van-der-Waals-Kraft: Die beiden Wafer werden dann in Kontakt gebracht, und die OH-Bindungen erleichtern ihre Verbindung durch die Van-der-Waals-Kraft.

Thermisches Ausglühen: Durch thermisches Glühen bei hoher Temperatur (1100 °C) werden die Wasserstoffionen ausgetrieben, wodurch die Bildung von Si-O-Si-Bindungen an der Grenzfläche gefördert und die Bindung verstärkt wird.

Rückätzung: Überschüssiges Silizium von einem Wafer wird durch Rückätzung entfernt, wobei die gewünschte Dicke der oberen Silizium-Dünnschicht zurückbleibt. Durch anschließendes Glühen und chemisch-mechanisches Polieren (CMP) wird eine glatte und saubere Oberfläche für die SOI-Wafer geschaffen.

Die BESOI-Technologie bietet mehrere Vorteile gegenüber der SIMOX-Technologie. So werden beispielsweise Probleme im Zusammenhang mit Injektionsschäden vermieden und die Bildung einer thermisch oxidierten vergrabenen Oxidschicht mit geringerer Defekt- und Pinhole-Dichte gewährleistet. Darüber hinaus besteht die durch BESOI hergestellte obere Siliziumschicht aus hochwertigem einkristallinem Silizium, was die Gesamtleistung des Bauelements verbessert.

Die BESOI-Technologie birgt jedoch auch Herausforderungen. Es ist schwierig, sehr dünne obere Siliziumschichten zu erzielen, und die Kontrolle von Grenzflächendefekten und der Homogenität der oberen Siliziumschicht bleibt eine Herausforderung. Darüber hinaus erfordert das Verfahren kostspielige Rückseitengravur- und CMP-Schritte, was zu einem erheblichen Verlust an Wafermaterial führt, das nicht wiederverwertet werden kann und zu höheren Produktionskosten beiträgt.

3.4.3 Smart-Cut-Technologie

Die Smart-Cut-Technologie ist von der BESOI-Technologie abgeleitet: Zunächst werden zwei Siliziumwafer vorbereitet; einer der Wafer wird thermisch oxidiert, um eine SiO2-Schicht zu bilden, und dann werden Wasserstoffionen in das Wafersubstrat injiziert; der andere Wafer muss nicht bearbeitet werden; ähnlich wie bei BESOI werden die beiden Wafer miteinander verbunden; nach dem Bonden brechen die mit Wasserstoffionen injizierten Wafer an der mit Wasserstoffionen angereicherten Grenzfläche durch eine thermische Reaktion bei 400-600 °C auf; schließlich bildet sich an der Grenzfläche zwischen der gebrochenen Oberfläche und der Oxidschicht nach einer Hochtemperaturbehandlung (1100 °C) zum Austreiben der Wasserstoffionen eine Siliziumfilmschicht. Nach dem Bonden brechen die mit Wasserstoffionen beaufschlagten Wafer an der Stelle, an der sich die Wasserstoffionen anreichern, und zwischen der Bruchfläche und der Oxidschicht bildet sich eine dünne Siliziumschicht. Nach der Hochtemperaturbehandlung (1100 °C) werden die Wasserstoffionen schließlich ausgetrieben, so dass sich an der gebondeten Grenzfläche eine Si-O-Si-Bindung bildet, die die chemische Bindung stärkt und die Qualität der dünnen Siliziumschicht verbessert; anschließend wird die Oberfläche durch CMP-Behandlung geglättet.

Smart-Cut ähnelt dem BESOI-Verfahren insofern, als die obere Siliziumschicht aus Bulk-Silizium besteht und die BOX-Schicht eine thermisch oxidierte Schicht ist. Die Dicke der BOX-Schicht und der oberen Siliziumschicht kann in einem weiten Bereich eingestellt werden, und die Dicke der oberen Siliziumschicht wird durch Nutzung der Energie der Ionenimplantation gesteuert, so dass eine sehr dünne und gleichmäßige obere Siliziumschicht erzielt werden kann. Außerdem kann das abgestreifte Wafermaterial wiederverwendet werden, was eine Kostenreduzierung ermöglicht.

-Siliziumwafer-Kristallpräparationsverfahren

Für die Züchtung von Siliziumkristallen wird häufig die Czochralski-Methode angewandt, bei der ein mit Silizium gefüllter Tiegel auf eine Temperatur von 1685 °C erhitzt wird. Diese Temperatur übersteigt den Schmelzpunkt von Silizium um etwa 100 °C, wodurch das Silizium im Tiegel geschmolzen wird. Im oberen Teil des Tiegels befindet sich ein Hebestab, der über eine mechanische Vorrichtung verfügt, die es ihm ermöglicht, sich frei zu heben und zu drehen. Auf dem Hebel ist ein kleines Stück einkristallines Silizium angebracht, das als "Keim" dient. Dieser Keimkristall löst die Anziehungskraft der umliegenden Siliziumatome aus, so dass sich diese zu einer Kristallstruktur organisieren. Während der Kristall allmählich aufsteigt und sich dreht, bleiben die entnommenen Abschnitte Teil desselben Einkristalls. Der resultierende große Einkristall misst bis zu 200 Millimeter im Durchmesser und ist damit dicker als ein durchschnittlicher Arm. Dieser Kristall weist keine Grenzflächen oder Defekte auf und verkörpert die höchste Perfektion, die bei von Menschen hergestellten Einkristallen erreicht werden kann.

Um die Reinheit des Materials zu gewährleisten und eine ungleichmäßige Keimbildung zu verhindern, müssen alle Vorgänge unter Vakuum oder Inertgas stattfinden. Bei den traditionellen Verfahren zum Heben von Einkristallen aus Silizium wird zu Beginn des Kristallwachstums eine dünne Einschnürung erzeugt, um Kristallversetzungen zu verhindern (Necking-Methode). Fortschritte in der Seeding-Technologie, insbesondere die Infusion einer beträchtlichen Menge an Bor in den Impfkristall, haben jedoch dessen Festigkeit drastisch erhöht, so dass eine Einschnürung mit einem Durchmesser von 3 mm nicht mehr erforderlich ist. Dieser innovative Ansatz ersetzt die drei Jahrzehnte alte Necking-Methode und erleichtert nicht nur die Produktion von großem einkristallinem Silizium, sondern verkürzt auch die Kristallwachstumszeiten und erhöht die Ausbeute, wodurch sich Möglichkeiten für die kosteneffiziente Produktion von integrierten Schaltkreisen im Ultra-Großformat eröffnen.

Beim Waferwachstum wird Polysilizium in einen Quarztiegel in einem Ofen eingefüllt und anschließend im Vakuum oder unter Inertgas gespült, um einen geschmolzenen Zustand zu erreichen. Sobald sich das geschmolzene Silizium stabilisiert hat, können Einkristalle gezogen werden, wobei die interne Kristallrichtung eines zuvor festgelegten Impfkristalls als Führung auf der Flüssigkeitsoberfläche dient. Durch die präzise Steuerung der Höhe der Flüssigkeitsoberfläche des Tiegels, der Temperatur der Fest-Flüssig-Grenzfläche und der Rotationsgeschwindigkeit des Impfkristalls wird das Silizium von der Flüssigkeit zurück in den Feststoff umgewandelt, wodurch eine einheitliche innere Kristallrichtung für das Wachstum von Einkristallen mit großem Durchmesser gewährleistet wird. Computergesteuerte automatische Anpassungsprozesse und Hubgeschwindigkeiten garantieren isotropes monokristallines Siliziumwachstum.

Tabelle 2 SOI-Wafer vs. Silizium-Wafer

|

Silizium-Wafer |

SOI-Wafer |

||

|

Aufbau |

Keine Isolierschicht |

Isolierende Schicht |

|

|

Leistung |

Unterdrückung von Crosstalk |

Nein |

Ja |

|

Geschwindigkeit und Leistung |

Niedriger und höher |

Höher und niedriger |

|

|

Strahlungswiderstand |

Niedriger |

Höher |

|

|

Anwendungen |

Integrierte Schaltungen |

Hochleistungsanwendungen |

|

|

Solarzellen |

Anwendungen mit geringem Stromverbrauch |

||

|

Biomedizinische Geräte |

Umgebungen mit hoher Strahlung |

||

|

Vorbereitung und Kosten |

SIMOX/BESOI/Smart-cut |

Czochralski-Verfahren |

|

|

Komplizierte |

Bequem |

||

|

Hohe Kosten |

Geringe Kosten |

||

4 Schlussfolgerung

Zwischen SOI- und Silizium-Wafern gibt es erhebliche Unterschiede in Bezug auf Materialstruktur, Leistungsmerkmale, Anwendungsbereiche usw. Die SOI-Struktur verbessert die Leistung und Zuverlässigkeit von Bauelementen durch eine schichtweise Siliziumschicht-Isolierschicht-Siliziumsubstrat-Struktur, allerdings zu höheren Herstellungskosten. Im Gegensatz dazu ist die herkömmliche Herstellung von Siliziumwafern weniger kostspielig und eignet sich für ein breites Spektrum der Herstellung integrierter Schaltungen. Daher sollten bei der Auswahl einer Materialstruktur die Vor- und Nachteile von SOI und Siliziumwafern auf der Grundlage spezifischer Anwendungsanforderungen und Kostenerwägungen umfassend bewertet werden, um die beste Leistung und den besten wirtschaftlichen Nutzen zu erzielen.

Weiterführende Lektüre:

Der Einfluss der Siliziumwaferqualität auf die Leistung und Zuverlässigkeit von Halbleitern

Referenzen:

[1]Jin W ,Wei C ,Wanghua Z , et al. Optimierung und umfassender Vergleich von thermo-optischen Phasenschiebern mit gefaltetem Wellenleiter auf SiN- und SOI-Plattformen[J]. Optics Communications, 2024, 555.

[2]Xin F ,Jiaqi N ,Shanglin Y , et al. Optische Kerbfilter mit abstimmbarer zentraler Wellenlänge und rekonfigurierbarem freien Spektralbereich auf SOI-Plattform[J]. Optics Communications, 2024, 554.

[3]N. V ,A. M ,I. K , et al. Novel crossbar array of silicon nitride resistive memories on SOI enables memristor rationed logic[J]. Solid State Electronics, 2024, 211.

Bars

Bars

Perlen & Kugeln

Perlen & Kugeln

Bolzen & Muttern

Bolzen & Muttern

Tiegel

Tiegel

Scheiben

Scheiben

Fasern & Stoffe

Fasern & Stoffe

Filme

Filme

Flocke

Flocke

Schaumstoffe

Schaumstoffe

Folie

Folie

Granulat

Granulat

Honigwaben

Honigwaben

Tinte

Tinte

Laminat

Laminat

Klumpen

Klumpen

Maschen

Maschen

Metallisierte Folie

Metallisierte Folie

Platte

Platte

Pulver

Pulver

Stab

Stab

Blätter

Blätter

Einkristalle

Einkristalle

Sputtering Target

Sputtering Target

Rohre

Rohre

Waschmaschine

Waschmaschine

Drähte

Drähte

Umrechner & Rechner

Umrechner & Rechner

Chin Trento

Chin Trento